TSMC Throws Shade At Intel's 18A Node As Being Inferior To Its 2nm Chip Tech

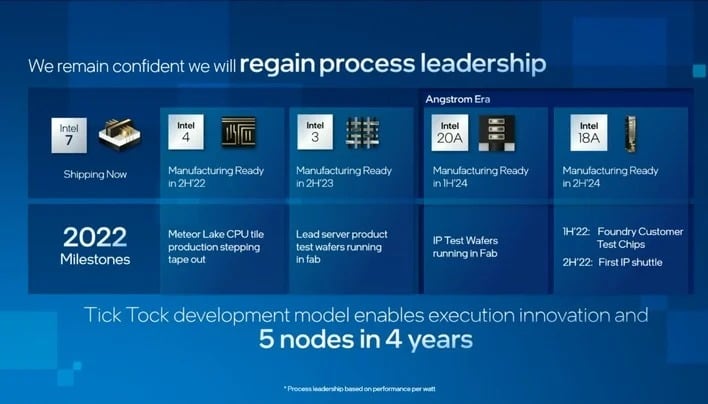

Intel hit a roadblock with its 10nm process, now known as "Intel 7", and then in the last few years, Intel hit another stumbling block with its Intel 4 process. The first parts on that technology will be the Meteor Lake chips launching in December. Intel CEO Pat Gelsinger clearly recognizes this as a major problem, as he committed last year to launching five process nodes in four years.

Well, Intel's main competitor in terms of fabrication technology is TSMC, and that company just held its Q3 quarterly earnings conference call. The prepared statements section of the call wasn't particularly interesting; HPC still accounts for nearly half of TSMC's revenue, and 59% of wafer revenue comes from 7nm-and-newer processes. TSMC enjoys high margins thanks to the extreme demand for its services, and its anticipates a Q4 operating margin of as high as 41.5%.

The really interesting part of TSMC's investor call comes at the beginning of the Q&A segment where an analyst for JP Morgan Chase and Company by the name of Gokul Hariharan throws TSMC's leadership a real hardball right out of the gate by asking if they think that TSMC will lose market share to Intel's IDM given Intel's aggressive plans for foundry expansion and development. He specifically notes Intel's plan to regain process technology leadership.

To his credit, TSMC CEO C.C. Wei didn't back down from the question at all. In fact, if anything, he may have said too much. His response, as reported by The Motley Fool, is included below:

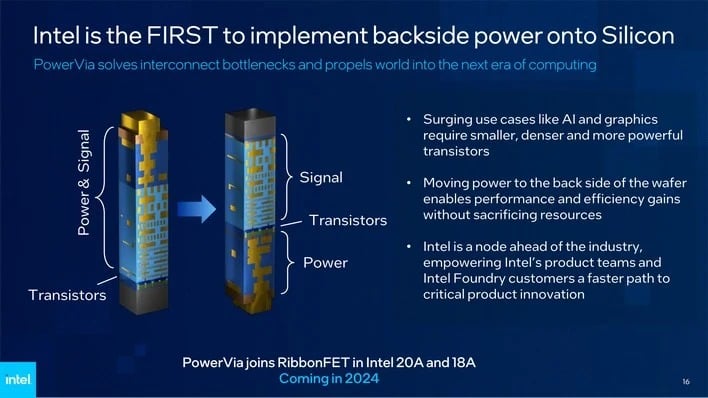

Actually, we do not underestimate any of our competitors or take them lightly. Having said that, our internal assessment shows that our N3P -- now, I'll repeat again, N3P technology, demonstrated comparable PPA to 18A, my competitors' technology, but with an earlier time to market, better technology maturity, and much better cost. In fact, let me repeat again, our 2-nanometer technology without backside power is more advanced than both N3P and 18A, and while the semiconductor industry is most advanced technology when it is introduced in 2025. Does that answer your question, Gokul?If you're not familiar with the jargon, PPA stands for Power, Performance, and Area, the three most important metrics for judging the quality of a manufacturing process. In other words, Dr. Wei is saying that he believes TSMC's next-gen leading-edge technology is equivalent not to Intel's upcoming Intel 4 process, nor its next 20A process, but its 18A process that isn't even scheduled to appear until 2025.

— Dr. C. C. Wei, TSMC Q3 2023 Earnings Call, via The Motley Fool

This is quite a claim. Dr. Wei surely knows more about both the technology and the business than we do, but even as outside observers, it's pretty surprising to hear. Intel's 20A process is going to introduce two major innovations in processor fabrication, those being RibbonFET Gate-All-Around (GAAFET) design and Intel's Backside Power Delivery Network (BSPDN). These two technologies are expected to radically improve the performance and efficiency of processors fabricated using them.

Whether those plans see fruition is another question altogether, of course. Many people have expressed skepticism at the aggressive pace that Gelsinger has set for Intel's foundry, but there's also the possibility that Dr. Wei brought up—the idea that even if Intel can keep its planned schedule, the results won't be market-smashing.

On the other hand, it's possible that Dr. Wei's comments are built on bravado born out of concern over Intel's rapid progress. On paper, the benefits of GAAFET construction and back-side power delivery seem like they would give Intel's processes a big advantage over TSMC's. Once again, though, only time will tell.